Módulo de Pre-procesamiento¶

Control de versiones¶

Desarrollo Primera Etapa¶

Responsable: Alan Aguilar

Revisión 1 - HW: No precisa

Revisión 2 - HW: No precisa

Desarrollo Segunda Etapa¶

Responsable: Luis Gonzales

Revisión 1 - HW: Se considerará como primera revisión de hardware la realizada por Luis Gonzales a la versión dejada por Alan Aguilar

Comentarios:

1. La memoria RAM utilizada IS62WV51216BLL tiene una velocidad de escritura y lectura máxima de 55ns que considerando el tiempo para entrar y salir de alta impedancia 20 ns, esto da una frecuencia de escritura de 13MHz pero en la implementación en VHDL estos tiempos se ampliaron para asegurarnos de la escritura o lectura de datos y dio un tiempo de 100ns aproximadamentr que equivale a 10MHz. Esto la hace mas lenta que la interfaz SPI hacia la Raspberry que usa un reloj de 16MHz y 8 bits de datos. La diferencia de velocidad hace que luego de recibir el comando de inicio del primer envío estará retrasada por toda una trama SPI.

Debido a que el envío SPI de la RPIB es de 8 bits por secuencia y la palabra de la memoria RAM puede ser de 24 o 16 bits lo cual hace posible el envío de dos o tres secuencias SPI por cada trama de memoria.

- Se han usado pines de la FPGA que no fueron diseñados para señales de reloj para la comunicación con los microcontroladores.

Revisión 2: Por definir

Funcionalidad¶

1.1 ¿Qué función realiza?

| Función | Descripción | Prueba de confiabilidad | |

|---|---|---|---|

| 1 | Recepción Nibbles | Captura nibbles desde el microcontrolador y los transforma en paquetes de 8, 16 o 24 bits | TBD |

| 2 | Decimación | Disminuye la tasa de transferencia de un canal al agrupar datos. | TBD |

| 3 | Almacenamiento en RAM | Almacenamiento de datos crudos y procesados | TBD |

| 4 | Comunicación SPI | Este módulo tendrá implementada la interfaz SPI en modo esclavo | TBD |

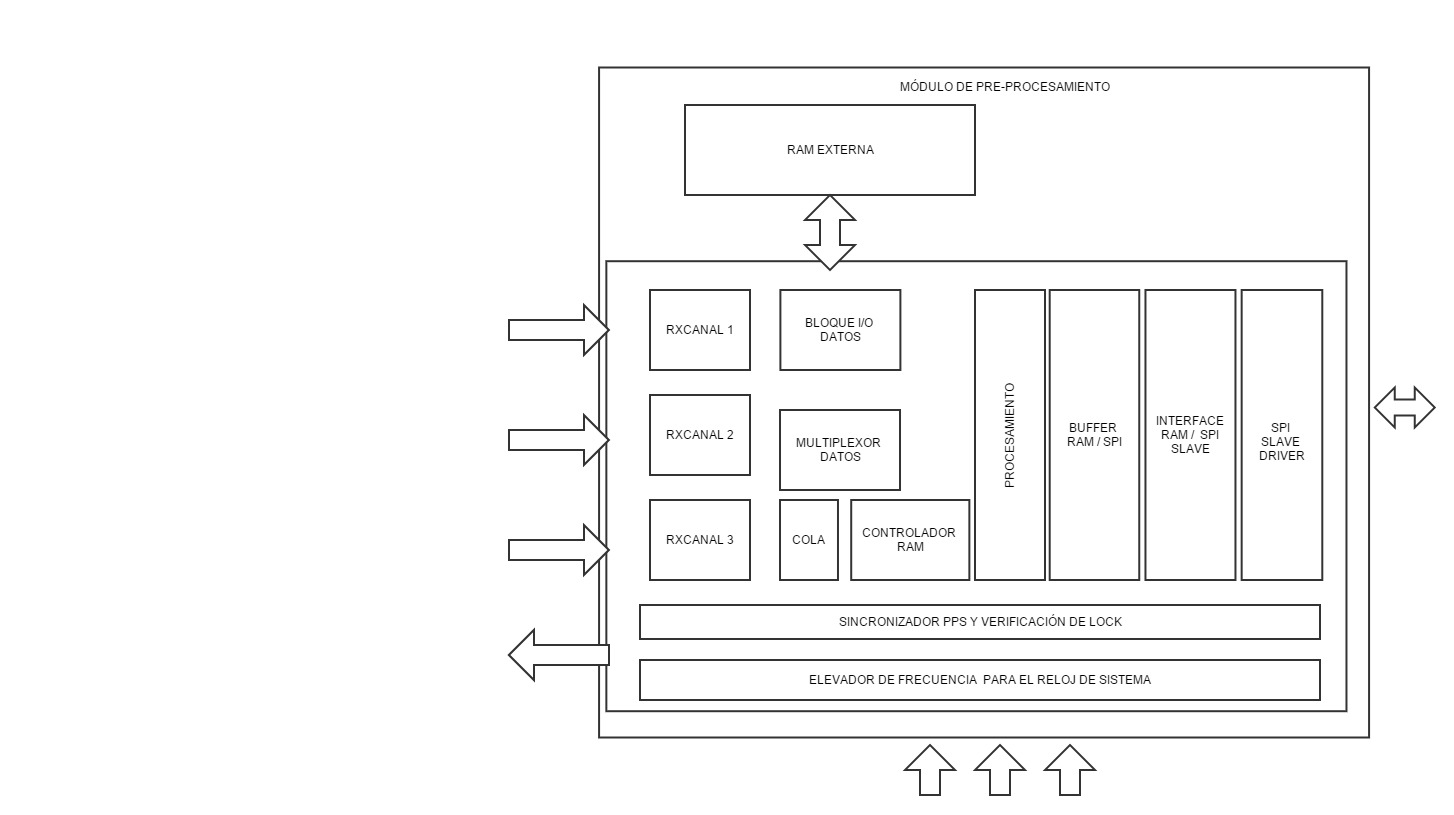

1.2 Existe un diagrama de bloques funcional? ¿Dónde?

Sí. Es el siguiente:

1.3 ¿El diseño cumple con todas las funciones requeridas? ¿Cómo?

Se han considerado desarrollar todos los componentes necesarios que ejecuten las funciones requeridas. Se han considerado los siguientes bloques:

| Componente | Función | Descripción | |

|---|---|---|---|

| 1 | Nibble / Paquete | Recepción de nibbles desde el microcontrolador | Transforma los envíos sucesivos de 4 bits en datos de 24 o 16 bits |

| 2 | Controlador RAM | Disminuye la tasa de transferencia de un canal al agrupar datos. | Genera las señales de control necesarias para la lectura y escritura en la Memoria RAM IS62WV51216BLL |

| 3 | Buffer Dato RAM - Dato SPI | Preparación de dato a ser enviado vía SPI | Este bloque tendrá preparado un dato leído desde la RAM de tal forma que cargue en un ciclo de reloj el dato hacia la interfaz SPI y una vez leído un dato solicitará un nuevo dato a la RAM. |

| 4 | Interfaz RAM - SPI | Puente entre el driver SPI esclavo y el dato RAM | Este módulo genera las señales de petición de dato al buffer RAM, une el dato desde RAM con la dirección del dato, separa el paquete dato+dirección en paquetes de 8 bits y reconoce el estado del driver SPI esclavo. |

| 5 | Driver SPI Esclavo | Envío y recepción de datos en modo SPI esclavo | Driver SPI esclavo de 8 bits por transmisión y carga de datos cada vez que CS_bar sea seleccionado. |

1.4 ¿Qué otras funciones puede realizar? ¿El diseño soporta nuevas funciones/entradas/salidas en un CPLD o FPGA?

Las funciones realizadas por este módulo puede ser la implementación de filtros analógicos o un pre procesamiento. Para esto nuevos componentes y diseños deben ser agregados.

La comunicación con el ADC y un posible pre-procesamiento sí podría ser realizado en una FPGA en reemplazo de los microcontroladores.

Robustez¶

2.1 ¿A qué tipo de entornos y condiciones será sujeto el circuito y cómo se evitará imprevistos?

| Entorno o condición | Descripción y Medidas | |

|---|---|---|

| 1 | Temperatura | -20°C a +50°C de temperatura ambiente. |

| 2 | Vibración | Vibraciones generadas por sismos. Muy esporádicas y baja frecuencia pero en ocasiones de gran amplitud. |

| 3 | Viento | El ambiente en el que será instalado todo el equipo puede ser de fuertes vientos pero el recubrimiento mecánico será diseñado para considerar efectos del viento. |

| 4 | Humedad | El ambiente en el que será instalado todo el equipo puede humedad relativa de entre 0 a 100% pero el recubrimiento mecánico será diseñado para considerar efectos debido a la humedad. |

| 5 | Polvo | El ambiente en el que será instalado todo el equipo puede ser en cerros o arenales pero el recubrimiento mecánico será diseñado para considerar efectos del polvo o partículas exteriores. |

| 6 | Interferencia electromagnética | El recubrimiento mecánico debe ser una jaula de Faraday para evitar corrientes inducidas por pulsos magnéticos generados por los rayos. |

| 7 | Shock electrostático (15kV) | En caso sea instalado en zonas de tormentas eléctricas o rayos, la estación debe contar con un pararrayos. Debido a que la antena GPS se conecta a una PCBA del sistema mediante un cable coaxial, las líneas de este cable están protegidas por un módulo que deberá ser instalado entre la PCBA y la antena con conexión a tierra. Este módulo de protección deberá contar ocn un "surge arrester" (GDT) y diodos de acción rápida. |

| 8 | Variación de voltaje | Se considera que las fuentes principales de energía son un cargador de baterías o un controlador de carga de batería para paneles solares o directamente las baterías. El rango de tensión de entrada es de 9 a 15VDC para el primer prototipo. Este rango de entrada requirió componentes "buck or boost converters" que finalmente alimentarán a reguladores LDO. Además el módulo de alimentación contará con una fuente de respaldo implementada con 2 súper condensadores. |

| 9 | Variación de corriente | El módulo de alimentación se encuentra monitoreando los niveles de tensión para que no haya requerimientos excesivos de corriente. |

2.1 ¿Hay márgenes de operación apropiados(50% del máximo para componentes)?

En este módulo se tienen dos integrados principales que son la FPGA y RAM externa los cuales sólo tienen condensadores asociados para desacoplo. El otro componente en este módulo es un regulador buck converter de 1.2VDC. Para evitar problemas de ruido debido al switching de este componente se sugiere usar todos los condensadores recomendados por el fabricante.

2.2 ¿Queda alguna entrada sin conectar en los componentes?

En la FPGA quedan algunos pines al aire pues no serán usados en ningún componente por lo que se espera que estos no originen problemas.

Consideraciones de diseño¶

Para el diseño de la PCB se tendrá en cuenta:

1. El pin por el cual ingresa la señal de reloj a la FPGA debe ser del tipo GCLK y soportar 3.3VDC.

2. Todos los pines de entrada salida con los cuales se trabajará deben soportar 3.3VDC.

3. Los pines que recibirán o generarán señales de reloj deberán ser del tipo GCLK.

4. Las pistas que transporten señales de reloj deben seguir el trayecto más corto posible y evitar estar cerca a otras señales como pistas de datos. En caso hayan cambios de sentido se deberán evitar ángulos rectos y de preferencia usar curvas.

5. Deberá considerarse los conectores para la programación JTAG del FPGA.

Durante la descripción de componentes en la FPGA deberá considerarse:

1. Usar primitivas especiales para las señales de reloj. Tanto para los multiplicadores, divisores y buffers conectados a los pines de entrada salida.

2. Para las señales de entrada/salida al FPGA considerar flip-flops de sincronismo para evitar estados de meta estabilidad.

3. En la detección de flancos de subida/bajada usar de preferencia dos flip-flops en cascada.

4. Procurar que todo el diseño sea con señales síncronas.

Hardware¶

La PCB diseñada por Alan Aguilar se encuentra en el siguiente enlace:

http://jro-dev.igp.gob.pe/svn/jro_hard/gen_acq/trunk/eagle/processingEngine/

VHDL - Descripción de hardware¶

Los componentes desarrollados se encuentran en el siguiente enlace:

Enlace Primera Etapa (Decimador y filtros):

http://jro-dev.igp.gob.pe/svn/jro_hard/gen_acq/trunk/firmware/sources/processingEngine/PrimeraEtapa/

Enlace Segunda Etapa (Bloques de comunicación):

http://jro-dev.igp.gob.pe/svn/jro_hard/gen_acq/trunk/firmware/sources/processingEngine/SegundaEtapa/

Notas¶

Referencias¶

A. Spartan 6 - Packaging and Pinout (Conocer qué pines son GCLK) : http://www.xilinx.com/support/documentation/user_guides/ug385.pdf

B. Spartan 6 - Datasheet (Conocer la velocidad máxima de reloj por primitivas y tiempos de setup, hold y delay):

http://www.xilinx.com/support/documentation/data_sheets/ds162.pdf

C. Spartan 6 - FPGA Configuration (Conocer configuración básica de primitivas y consideraciones de diseño):

http://www.xilinx.com/support/documentation/user_guides/ug380.pdf

D. Spartan 6 - FPGA SelectIO Resources (Conocer qué componentes usar en los pines de I/O):

http://www.xilinx.com/support/documentation/user_guides/ug381.pdf

E. Spartan 6 - FPGA Clocking Resources (Conocer la descripción de los pines de las primitivas de reloj):

http://www.xilinx.com/support/documentation/user_guides/ug382.pdf

F. Constraint Guide (Conocer las opciones de restricciones eléctricas y de tiempo para FPGA):

http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/cgd.pdf

G. Xilinx Timing Constraint User Guide:

http://www.xilinx.com/itp/xilinx10/books/docs/timing_constraints_ug/timing_constraints_ug.pdf

H. IS62WV51216BLL - Datasheet (Conocer los pines de I/O, las señales requeridas y tiempos necesarios para R/W):

http://www.issi.com/WW/pdf/62WV51216ALL.pdf