Módulo de Adquisición¶

Control de versiones¶

Desarrollo Primera Etapa¶

Responsable: Alan Aguilar

Revisión 1 - HW: No precisa

Revisión 2 - HW: No precisa

Desarrollo Segunda Etapa¶

Responsable: Luis Gonzales

Revisión 1 - HW: Se considerará como primera revisión de hardware la realizada por Luis Gonzales a la versión dejada por Alan Aguilar

Comentarios:

1. Las resistencias externas usadas para atenuar la señal de entrada de +/-10 y +/-5 hacen que disminuya el CMRR tal como indica la hoja técnica del AD8475.

2. Las resistencias externas usadas deben ser re calculadas en caso se mantengan en siguientes versiones. Esto pues la atenuación medida hace que el rango de salida del opamp sea menor que el rango de entrada del ADC.

3. Faltan condensadores de 0.1uF en AVDD1 y AVDD2.

4. Faltan condensadores de 1uF en REGCAP y REGCAPD.

5. Falta condensador de 0.1uF entre VDD y GND.

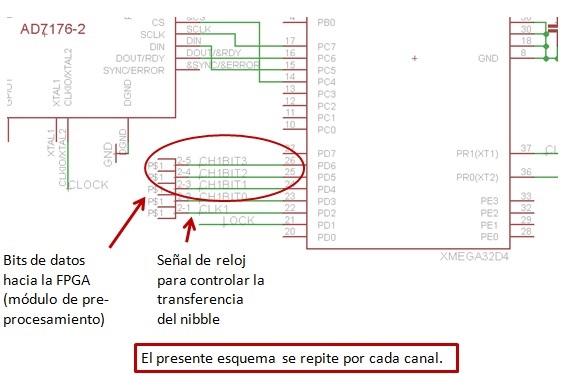

6. La justificación del porqué usar 3 micro controladores XMEGA en el módulo de adquisición sólo se justifica en que se considerará que la FPGA siempre recibirá 4 bits de datos y una señal de reloj para la transferencia de datos. Se justifica que sea de la familia XMEGA por una mayor frecuencia de operación y posibilidad de llevar algunos canales a consumo de muy baja energía en caso no sean usados.

Sugerencias

1. Todas las entradas deben estar desacopladas con 0.1uF a AVSS.

2. Se sugiere usar una referencia de 5V en la misma PCBA para el ADC. De esta forma se evita atenuar con resistencias externas la señal y no generará disminución del CMRR.

3. En el layout procurar mayor simetría de las entradas.

4. Separar en las entradas de +/-10 y +/-5 VDC.

5. Señalar que VCM es la tensión de modo común en el ADC.

6. Separar el ADC del microcontrolador.

7. Procurar aislar mediante tierras las señales entre canales.

Revisión 2: Por definir

Funcionalidad¶

1.1 ¿Qué función realiza?

| Función | Descripción | Prueba de confiabilidad | |

|---|---|---|---|

| 1 | Adecuación | Lleva la tensión de salida del sensor a niveles de tensión adecuados para el ADC. Así como el modo común, impedancia de entrada y salida. | TBD |

| 2 | Digitalización | Transforma la señal analógica en una señal digital de 24 bits tomando 250k muestras por segundo. | TBD |

| 3 | Paso a formato estándar | Lleva la codificación en el formato enviado por el ADC a un formato que será estándar para la comunicación con el módulo de pre-procesamiento. | TBD |

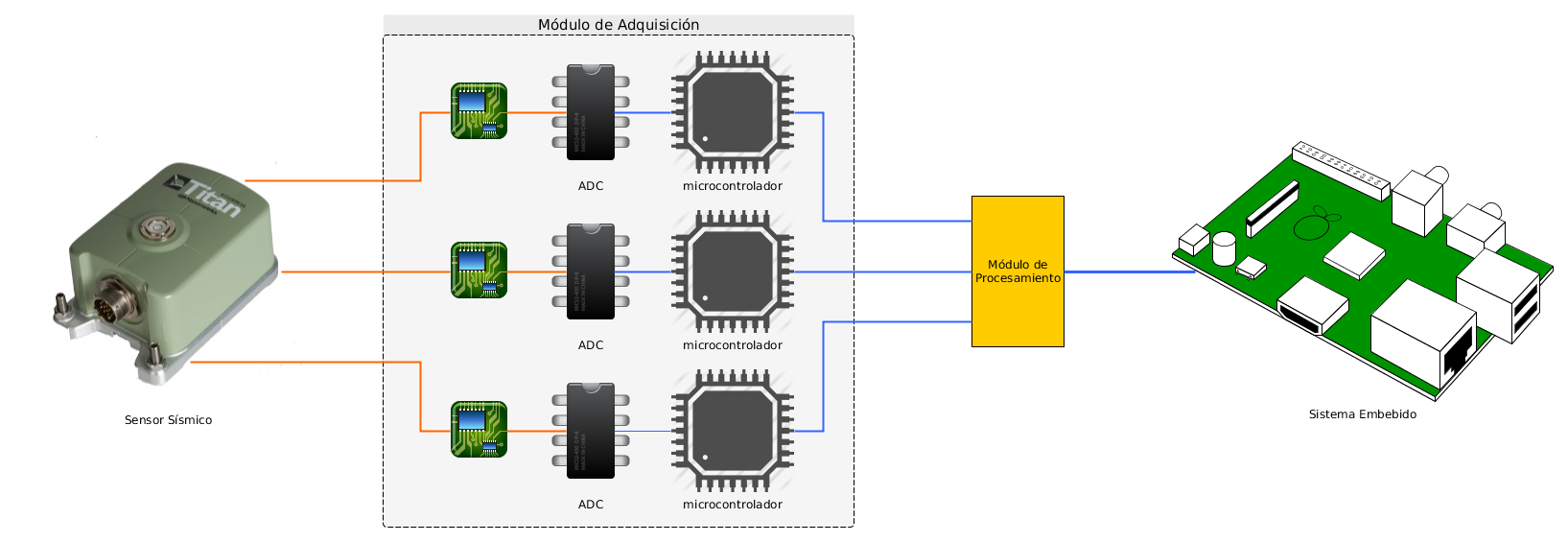

1.2 Existe un diagrama de bloques funcional? ¿Dónde?

Sí. Es el siguiente:

1.3 ¿El diseño cumple con todas las funciones requeridas? ¿Cómo?

Para la prueba del primer prototipo se usó el atenuador (AD8475) que brinda la posibilidad de bajar una tensión diferencial o de salida única de +/-10VDC o +/-5VDC a una salida diferencial +/-4VDC con un modo común ajustable y una impedancia de salida adecuada para el ADC (AD7176-2). Este ADC tiene un rango de frecuencia de muestreo desde los 5ksp hasta los 250ksps con una resolución de hasta 24 bits útiles a 5ksps y 17 bits útiles en el rango pico pico a 250ksps.

Los requisitos de prueba para este módulo son los de poder digitalizar en 24 bits señales diferenciales.

En el alcance del primer prototipo se realizarán las pruebas con el magnetómetro patentado por el ROJ.

1.4 ¿Qué otras funciones puede realizar? ¿El diseño soporta nuevas funciones/entradas/salidas en un CPLD o FPGA?

Las funciones realizadas por este módulo puede ser la implementación de filtros analógicos o un pre procesamiento. Para esto nuevos componentes y diseños deben ser agregados.

La comunicación con el ADC y un posible pre-procesamiento sí podría ser realizado en una FPGA en reemplazo de los microcontroladores.

Robustez¶

2.1 ¿A qué tipo de entornos y condiciones será sujeto el circuito y cómo se evitará imprevistos?

| Entorno o condición | Descripción y Medidas | |

|---|---|---|

| 1 | Temperatura | -20°C a +50°C de temperatura ambiente. |

| 2 | Vibración | Vibraciones generadas por sismos. Muy esporádicas y baja frecuencia pero en ocasiones de gran amplitud. |

| 3 | Viento | El ambiente en el que será instalado todo el equipo puede ser de fuertes vientos pero el recubrimiento mecánico será diseñado para considerar efectos del viento. |

| 4 | Humedad | El ambiente en el que será instalado todo el equipo puede humedad relativa de entre 0 a 100% pero el recubrimiento mecánico será diseñado para considerar efectos debido a la humedad. |

| 5 | Polvo | El ambiente en el que será instalado todo el equipo puede ser en cerros o arenales pero el recubrimiento mecánico será diseñado para considerar efectos del polvo o partículas exteriores. |

| 6 | Interferencia electromagnética | El recubrimiento mecánico debe ser una jaula de Faraday para evitar corrientes inducidas por pulsos magnéticos generados por los rayos. |

| 7 | Shock electrostático (15kV) | En caso sea instalado en zonas de tormentas eléctricas o rayos, la estación debe contar con un pararrayos. Debido a que la antena GPS se conecta a una PCBA del sistema mediante un cable coaxial, las líneas de este cable están protegidas por un módulo que deberá ser instalado entre la PCBA y la antena con conexión a tierra. Este módulo de protección deberá contar ocn un "surge arrester" (GDT) y diodos de acción rápida. |

| 8 | Variación de voltaje | Se considera que las fuentes principales de energía son un cargador de baterías o un controlador de carga de batería para paneles solares o directamente las baterías. El rango de tensión de entrada es de 9 a 15VDC para el primer prototipo. Este rango de entrada requirió componentes "buck or boost converters" que finalmente alimentarán a reguladores LDO. Además el módulo de alimentación contará con una fuente de respaldo implementada con 2 súper condensadores. |

| 9 | Variación de corriente | El módulo de alimentación se encuentra monitoreando los niveles de tensión para que no haya requerimientos excesivos de corriente. |

2.1 ¿Hay márgenes de operación apropiados(50% del máximo para componentes)?

Fueron considerados por Alan Aguilar en las potencias de las resistencias o tensión de condensadores asociados al ADC y OPAMP.

2.2 ¿Queda alguna entrada sin conectar en los componentes?

En el microcontrolador, OPAMP y ADC. Pero se deberán configurar como entradas los pines del microcontrolador y en el OPAMP o ADC se deberán colocar los condensadores recomendados por el fabricante.

Consideraciones de diseño¶

Entradas¶

- Sensor considerado para las pruebas : Magnetómetro ROJ

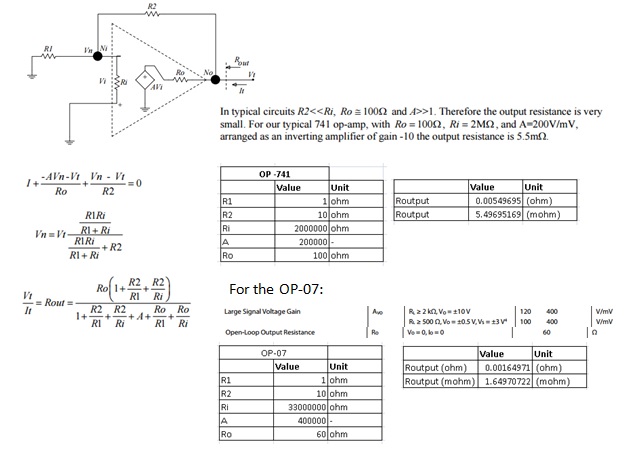

- Etapa de salida OP-07 en modo seguidor

- Rango de tensión de salida del sensor +/-10VDC

- Tasa de muestreo en el orden de las unidades de kHz

- Impedancia de salida del magnetómetro en seguidor: 2mohm aprox

(Suponiendo R1 = 1 y R2 = 10)

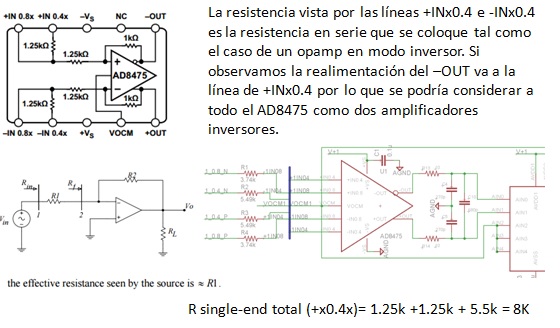

* Elemento de entrada del Sistema: AD8475

-Consumo eléctrico: 3.2mA @ 5VDC

-Impedancia de entrada

(Sin las resistencias externas):

--Entrada terminación única: 2.92kohm

--Entrada diferencial: 5kohm

--Atenuación: x0.4 = 1k/(1.25k+1.25k)

(Con las resistencias externas 5.5kohm en las líneas de x0.4):

--Entrada terminación única: 8.5kohm

--Entrada diferencial: 17kohm

--Atenuación: x0.12 = 1k/((1.25k+1.25k)+5.5k)

- Tensión máxima de modo común en las líneas de entrada: Vs/2 = 2.5VDC

Salidas¶

- Elemento de salida del módulo: Salidas digitales del XMEGA32D4

- Impedancia de salida

- Nivel de tensión de salida 3.3VDC

- Número de bits transmitidos por flanco de reloj: 4 bits

- La señal de control de transferencia de nibble es de 8MHz como máximo.

Parámetros en el ADC¶

AD7176-2

* Parámetros de eléctricos

- Tipo de entradas disponibles: Existen 5 líneas de ingreso de señal AIN0-AIN5

- Tipo de entrada usada: Diferencial AIN0 y AIN1

- Alimentación: 5VDC etapa analógica - 3.3VDC etapa digital

- Consumo: 2.6mA@3.3VDC - 7.2mA {2.1mA[AVDD]+5.1mA[AVDD2]]}@5VDC

- Rango entrada máximo: +/- Vref(2.5VDC de referencia interna)

- Frecuencia de reloj: 16MHz

- Duty Cycle de reloj: 30% - 70%

- Frecuencia de muestreo: Configurable - Rango: [5;250] ksps

- Número de bits útiles en la digitalización: Depende del filtro seleccionado y tasa de transmisión (17 bits para 250ksps en filtro Sinc5+Sinc1)

- Características de la interfaz de comunicación

- Interfaz de comunicación: SPI

- Modo de SPI: 0 {Modo Idle de SCK en Alta - Cambio de dato en flanco de bajada - Lectura de dato en flanco de subida }

- Frecuencia máxima de reloj SCK (Tabla 2 de la Hoja Técnica): 20MHz

- Número de bits por transmisión: Variable dependiendo del comando

- Número de bits por muestra: Configurable entre 24 o 16 bits

- Nota 1: La configuración de las líneas usadas por cada canal y su polaridad es seleccionable en el registro CHMAP0-3. En este registro se habilitan o deshabilitan canales.

- Nota 2: Cada canal mapeado es asociado a un registro de Setup de configuración. En este registro se selecciona si la salida considerará con o sin offset(bipolar). También se selecciona qué referencia de voltaje se usa en las conversiones.

- Nota 3: Un tercer registro es usado para seleccionar el filtro y la tasa de muestreo. Estos registros son los FILTCON0-3.

- Nota 4: Existen dos registros adicionales que pueden ser ajustados para una mejor conversión: offset y gain. Estos son factores de corrección cuya intención es eliminar los errores de conversión.

Parámetros en el microcontrolador¶

- Código: XMEGA32D4

- Tensión de alimentación: 3.3VDC

- Frecuencia de operación 32MHz

- Reloj SPI: 16MHz

- Número de bits por TX/RX SPI: 8 bits

Hardware¶

Enlace¶

Los archivos en Eagle de la versión fabricada se encuentran en el siguiente enlace:

http://jro-dev.igp.gob.pe/svn/jro_hard/gen_acq/trunk/eagle/acquisition/

Firmware¶

Enlace¶

El proyecto en Atmel Studio 7.0 se ecuentra en el siguiente enlace URL:

http://jro-dev.igp.gob.pe/svn/jro_hard/gen_acq/trunk/firmware/sources/acquisitiond/Segunda_Etapa/Ver_2/

Notas¶

- En esta versión el micro controlador envía la señal de reloj a la FPGA luego de cada conversión.

Referencias¶

A. AD8476 - Hoja técnica atenuador: http://www.analog.com/media/en/technical-documentation/data-sheets/AD8475.pdf

B. AD7176-2 - Hoja técnica ADC: http://www.analog.com/media/en/technical-documentation/data-sheets/AD7176-2.pdf

C. Nota de aplicaciones - AD8475+AD7176-2 - CN0310: http://www.analog.com/media/en/reference-design-documentation/reference-designs/CN0310.pdf

E. Effective bits and Peak to Peak Resolution: http://www.analog.com/media/en/technical-documentation/application-notes/AN-615.pdf?doc=CN0383.pdf